Lvds что это в телевизоре

Обновлено: 18.05.2024

Разрядность и быстродействие контроллеров, процессоров и изделий на их основе постоянно возрастают. Производительность всей системы сильно зависит от скорости обмена данными между устройствами. В последнее время для этого вс╦ чаще используют высокоскоростные интерфейсы LVDS (Low-Voltage Differential Signaling или дифференциальный метод передачи с использованием сигналов низкого уровня) и M-LVDS (Multipoint-LVDS или многоточечный двунаправленный способ обмена информацией). Они позволяют организовать сверхскоростной обмен между микросхемами на печатной плате, а также эффективное взаимодействие между блоками и стойками. На передающей стороне параллельный код преобразуется в последовательный. На принимающей - выполняется обратное преобразование информации. Такой способ обмена позволяет существенно уменьшить количество соединительных проводников, сократить габариты разъемов при увеличении надежности и уменьшении стоимости всего комплекса.

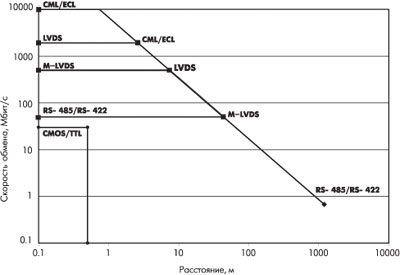

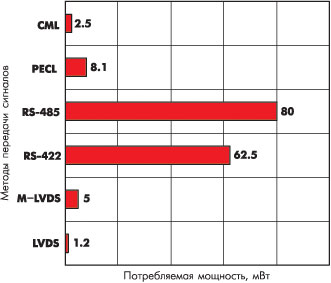

На рис. 1 показаны соотношения скорости обмена и допустимого расстояния для разных интерфейсов. Обратите внимание, что масштаб по осям логарифмический! Из рис. 1 очень хорошо видно, что каждый тип интерфейса имеет свою нишу и предназначен для определенных областей применения. Основное назначение любого последовательного интерфейса - "сворачивание" параллельного кода в скоростной последовательный канал и "разворачивание" последовательного кода в параллельный на приемной стороне.

При расстояниях до 30 м и скоростях передачи менее 50 Мбит/с обычно используют интерфейсы стандартов TIA/EIA-422 (RS-422, multidrop) и TIA/EIA-485 (RS-485, multipoint). Выходные дифференциальные сигналы высокого уров-ня, чувствительные приемники и работоспособность при уровнях помех до 7 В - их положительные качества для обеспечения эффективного обмена данными между удаленным оборудованием. Для скоростей передачи более 50 Мбит/с или в устройствах, где очень важно низкое потребление энергии, применяют интерфейсы LVDS или M-LVDS. Передача и прием со скоростью около 10 Гбит/с обеспечивается эмиттерно-связанной логикой (ECL - emitter-coupled logic) или положительной эмиттерно-связанной логикой (PECL - positive ECL). Однако такая высокая скорость обмена достигается за счет увеличения стоимости при сильном росте потребляемой мощности.

Немаловажным параметром является экономичность каждого типа интерфейса. На рис. 2 показана диаграмма потребления мощности некоторыми интерфейсами и типами логики. Стоит отметить, что LVDS и M-LVDS занимают лидирующие позиции по этому параметру. Вдобавок к этому, только что отмеченные интерфейсы работоспособны при самых низких питающих напряжениях среди показанных на рис. 2.

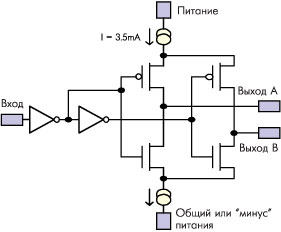

Благодаря токовому выходу оконечного каскада (рис. 3), потребляемая мощность LVDS и M-LVDS практически не зависит от скорости передачи информации.

Эти положительные особенности особенно важны для автономных и портативных устройств. Сигналы низкого уровня и дифференциальная схема передачи существенно облегчают решение проблемы электромагнитной совместимости, что добавляет очки в копилку положительных качеств рассматриваемых интерфейсов LVDS и M-LVDS.

На рис. 4 показан обзор микросхем интерфейсов LVDS фирмы Texas Instruments. Некоторые из них позволяют получить скорость обмена до 2 Мбит/c. Но как для спортивного скоростного автомобиля требуется специальная трасса, так и для достижения сверхвысоких скоростей обмена данными необходим тщательный подход к проектированию всего тракта передачи и приема.

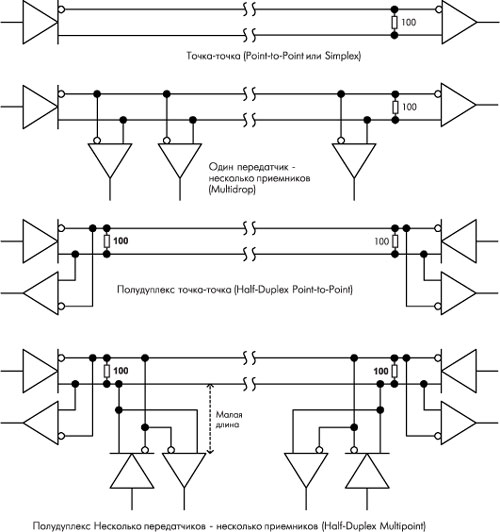

На рис. 5 показаны возможные способы обмена между устройствами. Simplex (точка-точка) позволяет передавать информацию только в одну сторону и только одному приемнику. На приемной стороне тракта передачи обязательно наличие согласующего резистора (терминатора). Вариант Multidrop содержит в своем составе один передатчик и несколько приемников (каждый из них располагается рядом с основной линией передачи). И в этом случае необходимо наличие только одного резистора для устранения отраженных сигналов.

Полудуплекс позволяет организовать двухсторонний обмен данными, но с разделением во времени, то есть в любой момент времени передача информации может происходить только в одном направлении (отсюда и приставка полу-). При полудуплексе точка-точка обмен происходит только между двумя устройствами. При многоточечном полудуплексе (Multipoint) двухсторонний обмен возможен между любыми устройствами, но опять же с условием временного разделения потоков информации. В этом случае терминальные резисторы должны быть установлены на обеих сторонах основного канала передачи и приема (рис. 5).

Интерфейсы LVDS (один передатчик - несколько приемников, стандарт TIA/EIA-644) не позволяют напрямую организовать двунаправленный многоточечный обмен, как это возможно с помощью интерфейсов RS-485 (стандарт TIA/EIA-485). Для создания многоточечного полудуплексного режима "Несколько передатчиков - несколько приемников на одной шине" фирмами Texas Instruments и National Semiconductor был создан многоточечный интерфейс M-LVDS (стандарт TIA/EIA-899-2001), с помощью которого возможен двухсторонний обмен данными (Half-Duplex Multipoint - многоточечный полудуплекс). M-LVDS - это высокоскоростной экономичный многоточечный RS-485, позволяющий создать сеть, включающую в себя до 32 узлов со скоростью обмена до 500 Мбит/c.

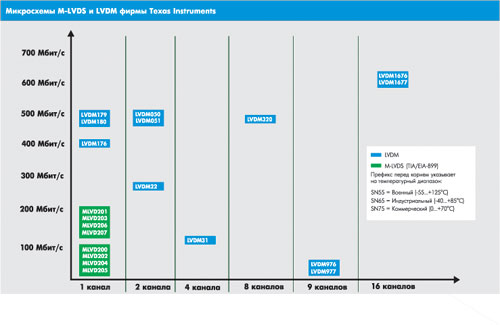

На рис. 5 представлены микросхемы M-LVDS и LVDM интерфейсов Texas Instruments.

Интерфейсные микросхемы LVDM имеют в два раза более мощный токовый выход. Это необходимо при работе на линию с двумя согласующими резисторами (полудуплексный обмен). Эти приборы были специально разработаны для создания скоростной шинной архитектуры M-LVDS. У фирмы National Semiconductor подобные микросхемы называются BusLVDS или BLVDS. Для LVDM и BusLVDS выходной ток лежит в пределах от 8 до 10 мА. Для M-LVDS - около 11 мА.

В номенклатуре Texas Instruments есть и LVDT-интерфейсы. Наличие буквы "Т" говорит о том, что внутри микросхемы имеется встроенный согласующий резистор (терминатор) сопротивлением около 100 Ом. Следует учесть, что LVDT-микросхемы можно устанавливать только на оконечных (основных) узлах основного тракта, так как на промежуточных узлах согласующие резисторы не нужны.

В табл. 1 приведены основные типы микросхем для шинной архитектуры M-LVDS.

В табл. 2 показано соответствие между некоторыми микросхемами интерфейсов LVDS и M-LVDS ведущих мировых производителей.

Fairchild - Fairchild Semiconductor; NSC - National Semiconductor; Maxim - Maxim

Integrated Products; Philips - Philips Semiconductors; Pericom - Pericom Semiconductor.

*) F - функционально близкий, но не полный эквивалент; P - близкое соответствие, но не pin-for-pin (отличаются расположением выводов); Q - близкая функциональность и совпадение по выводам, но не полный эквивалент; S - полное совпадение по функциональности и по выводам.

Каналы LVDS и M-LVDS имеют в своей основе недорогие материалы (легко создаются на печатной плате или с помощью широко распространенного кабеля CAT5). Рассмотренные скоростные интерфейсы выпускаются многими известными компаниями, что значительно расширяет выбор при построении скоростной сети различного уровня сложности.

При необходимости Вы можете обратиться в центр информационно-технической поддержки (EPIC) фирмы Texas Instruments.

За дополнительной информацией обращайтесь к сотрудникам фирмы КОМПЭЛ по адресам:

В предыдущей части статьи были рассмотрены общие принципы работы LVDS-канала, его составные части и общие параметры. Сейчас мы продолжим описание рекомендаций по разработке LVDS-интерфейсов.

В предыдущей части статьи были рассмотрены общие принципы работы LVDS-канала, его составные части и общие параметры. Сейчас мы продолжим описание рекомендаций по разработке LVDS-интерфейсов. Общие требования и требования к топологии печатных плат были описаны ранее. Теперь приведем рекомендации для оставшихся составных частей LVDS-канала — разъемов и соединительных кабелей.

Кабели

Соединительные кабели являются важной частью LVDS-канала. От их параметров во многом зависит скорость и надежность передачи данных. При выборе кабеля желательно соблюдать ряд рекомендаций. Всегда надо помнить, что кабель и соединительные разъемы должны образовывать согласованную систему передачи с дифференциальным сопротивлением, максимально приближенным к 100 Ом. Для передачи дифференциального интерфейса LVDS желательно использовать сбалансированные симметричные кабели типа витой пары. Такие кабели позволяют достичь лучшего качества передаваемого сигнала за счет постоянного сопротивления и идентичности влияния внешних наводок, которые подавляются на приемном конце, на витую пару. Кроме того, симметричные пары имеют меньшее излучение, что благоприятно сказывается как на общем уровне наводок системы, так и на качестве передачи за счет снижения уровня перекрестных наводок.

Стандартом LVDS тип и параметры кабеля и соединителей жестко не регламентируются. Однако в нем есть ссылки на сопутствующие документы, определяющие требования к параметрам кабеля, разъемов, разбивки по контактам и т. п.

Выбор типа кабеля во многом зависит от требуемой дальности и скорости передачи. На дистанциях до 0,5 м. подходят практически все типы кабелей. С соблюдением ряда требований, которые будут раскрыты ниже, можно использовать недорогие и популярные плоские кабели (шлейфы) и распространенные в портативных устройствах ленточные кабели.

Плоский кабель (шлейф), хотя и не является идеальным решением для высокоскоростных интерфейсов, однако имеет реальное применение. Для плоского кабеля рекомендации просты и очевидны из рисунка 8. Сигнальные линии одной дифференциальной пары должны располагаться рядом. Между разными парами помещается разделительный заземленный провод. Не рекомендуется располагать сигнальные линии крайними — для них должно быть сделано обрамление из заземленных проводов. Общая рекомендация — кабель желательно поместить в заземленный экран.

При использовании ленточного кабеля следует соблюдать те же правила, что и для согласованной линии на печатной плате (рис. 6, a).

На дистанциях от 0,5 до 10 м. очень хорошо зарекомендовали себя широко используемые недорогие и доступные кабели типа витая пара — CAT3, CAT5 и CAT5Plus. Получаемые с использованием таких кабелей параметры линии позволяют передавать данные с удовлетворением всех требований стандарта по одной паре со скоростью до 400 Мбит/c на расстояние до 10 м. В качестве примера приведем данные по разбросу фронтов для неэкранированного кабеля CAT5.

Как видно из рисунка 9, графики дрожания фронтов для разной длины кабеля расположены близко друг от друга и практически параллельны. Очевидно, что для согласованной симметричной линии качество мало зависит от длины линии, а в гораздо большей степени от ее частотных параметров, в данном случае граничной частоты.

Теперь рассмотрим доступность таких кабелей. Кабель типа CAT5 — тот самый кабель, который применяется при построении сетей Ethernet и содержит пять витых пар. Он имеется в продаже и стоит около 0,3 $ за метр. Если по одной паре можно обеспечить передачу на скорости до 400 Мбит/c, то скорость передачи по пяти парам эквивалентна практически 2 Гбит/c на расстояние 10 м. Это данные для базового типа кабеля CAT5 с параметрами, определенными до 100 МГц, а ведь уже существуют кабели CAT5+ с параметрами, определенными до 350 МГц, и кабели типа CAT6. Последний тип кабелей выпускается во всевозможных модификациях с экранированием и без, также для различных условий эксплуатации. Его использование также подразумевает наличие разнообразного и массово выпускаемого ассортимента разъемов и сопутствующих монтажных материалов и инструментов, а также наличие наработанных решений по разводке и монтажу.

Еще одним менее распространенным, но применяемым в скоростных решениях является попарно экранированный (twin-ax) кабель (рис. 10)

Он обеспечивает большее разделение пар и лучшие условия передачи, что позволяет достигать предельно возможных для стандарта значений скорости, дальности и надежности передачи.

Приведенные данные касаются кабеля, который является важной, но одной из составляющих LVDS-канала. Следует помнить, что и остальные части — разводка платы и разъемы, должны быть выдержаны в рамках требований стандарта.

Разъемы

При построении LVDS-линков можно использовать различные типы соединительных разъемов. Конкретный тип разъема определяется требуемыми параметрами линии, скоростью передачи и типом используемого кабеля.

Необходимо учитывать, что LVDS — скоростной интерфейс, использующий достаточно высокие частоты, и поэтому требуется выбирать соответствующие разъемы. Рекомендуется группировать пары LVDS-линий для уменьшения как внешних наводок на LVDS- канал, так и электромагнитных излучений. LVDS — дифференциальный интерфейс, и оба его провода должны располагаться в максимально идентичных условиях.

Далее отметим характерную именно для LVDS особенность выбора расположения сигнальных линий на контактах разъема — различные выводы разъемов могут иметь различную длину, что приводит к потенциальным искажениям LVDS-сигнала, как показано на рис. 11. При построении LVDS-линий, особенно скоростных, рекомендуется выбирать для проводов одной пары максимально идентичные по длине выводы.

На разъеме (см. рис. 11) LVDS-линии расположены правильно, а на нижнем разница в длине выводов разъема может вызвать потенциальные искажения. В настоящее время существуют даже специально разработанные для LVDS разъемы, у которых выводы разбиты на пары и разделены экранирующими контактами. На рис. 12 показан пример такого разъема, выпускаемого фирмой TERADYNE.

Как иллюстрацию влияния приведенных выше правил приведем пример тестовых испытаний, проведенных фирмой AMP для своих разъемов серии MICTOR. При этом тестировании проводились оценки взаимовлияния LVDS-пар при различном взаимном расположении их на разъеме. На рис. 13 показаны три варианта расположения LVDS-пар на разъеме.

Рис.13. Три варианта расположения LVDS- линий на разъеме:

a — рекомендованное расположение

б — две пары не разделены экраном

в — максимально уплотненные пары

Для каждого из трех случаев измерялся уровень взаимных наводок на ближнем и дальнем конце кабеля, которые и показаны на рис. 14. При этом на соседние пары подавались сигналы со сдвигом 0,05 нс амплитудой 400 мВ и временем нарастания/спада (1/9) 0,25 нс.

На рис. 14, а показаны уровни наводок на ближнем и на рис. 14, б — на дальнем конце кабеля. Красным цветом выделена кривая дифференциального шума для случая расположения LVDS-линий, как показано на рис. 13, а; зеленым цветом — для случая показанного на рис. 13, б; синим цветом — на рис. 13, в.

Из графиков видно, что несоблюдение рекомендаций по расположению и экранированию LVDS- линков увеличивает уровень перекрестных наводок в несколько раз, это существенно снижает возможную скорость передачи данных по каналу.

Подача и снятие потока данных

Еще одним из факторов, определяющих быстродействие LVDS-интерфейса, а также одной из проблем разработки скоростных каналов является проблема подвода потока данных, как правило, по-обычному TTL или LVTTL-интерфейсу к LVDS-передатчику. Для решения этой проблемы уже выработан ряд технологических приемов. Во-первых, наборы для построения LVDS-каналов строятся уже не на базе отдельных LVDS-передатчиков, а на базе микросхем сериалайзеров — параллельно-последовательных преобразователей, преобразующих сигналы от нескольких параллельно подводимых линий в один высокоскоростной LVDS-канал. На приемном конце, в свою очередь, устанавливается десериалайзер — чип обратного преобразования из последовательного канала в параллельный. Использование, например, 10-разрядного сериалайзера позволяет при канале со скоростью 622 Мбит/c снизить частоту подводимых данных до 62,2 МГц, что вполне приемлемо с точки зрения использования TTL-интерфейса.

Еще одним вариантом решения проблемы подачи и снятия данных для LVDS является интеграция LVDS-приемников и передатчиков непосредственно в состав устройств источников и приемников данных. Так, производитель программируемой логики фирма Xilinx интегрирует в состав FPGA последних семейств определенное количество LVDS-портов. Такой вариант имеет и еще одно функциональное преимущество: сочетание в одном корпусе программируемой логики и LVDS-интерфейсов позволяет легко выполнять построение LVDS-каналов требуемой архитектуры, скорости и типа внешнего интерфейса.

Шинные LVDS-решения

Кроме передачи точка — точка, топология интерфейса LVDS предусматривает еще ряд возможных топологий, показанных на рис. 15.На рис. 15, a показана базовая топология точка — точка, которую мы уже рассматривали ранее. На одну линию можно подключить не один, а несколько приемников при одном LVDS-передатчике и получить топологию точка — многоточка (multidrop), показанную на рис. 15, б. При этом линия терминируется на одном приемном конце.

Рис. 15. Возможные топологии LVDS-канала

a — точка — точка (point-to-point)

b — точка — многоточка (multidrop)

c — шинная топология (multipoint)

Возможность подключения на одну пару нескольких приемников и нескольких передатчиков позволяет организовывать на базе LVDS-стандарта шинные решения с использованием всех его преимуществ. На рис. 15, в, каждая линия шины представляет собой согласованную 100-омную линию с терминаторами на концах. На эту линию подключается несколько LVDS-приемников и несколько LVDS-передатчиков. При таком включении по одной паре LVDS возможна организация двухстороннего полудуплексного канала, то есть в каждый момент времени активен только один из передатчиков. Для удобства построения шин выпускаются микросхемы, которые включают в себя и передатчик и приемник для каждой пары внешних LVDS-выводов.

Применение LVDS

Рассмотрев особенности построения самих LVDS-каналов, приведем несколько конкретных примеров LVDS-решений.

Скоростной многоканальный LVDS-линк на базе FPGA Virtex-E фирмы Xilinx

Для примера приведем структуру построения скоростного 622 Мб/с LVDS-канала на базе ПЛИС Xilinx серии Virtex-E. Особенностью данного примера является передача параллельного потока данных, непосредственно между ПЛИС Xilinx с использованием встроенных LVDS-приемопередатчиков.

Рис. 16. Построение законченного LVDS-канала из двух каналов данных по 622Мбит/c и одного тактового сигнала

На рис. 16 показана схема построения законченного LVDS-канала из двух каналов данных по 622 Мбит/c и одного тактового сигнала частотой 311 МГц. При передаче используются оба фронта тактового сигнала. Задержки сигнала такта и данных одинаковы, поскольку эти сигналы генерируются одинаковыми мультиплексорами. Терминирование передатчиков со стороны источника приводит уровни в полное соответствие со стандартом LVDS и согласует выходы с используемой в данном примере 50-омной несимметричной или 100-омной симметричной линией. Параллельные терминаторы на приемном конце в соответствии со стандартом LVDS представляют собой 100-омные резисторы (рис. 17).

Для обеспечения лучших условий приема тактовый сигнал задерживается на 1,1 нс с использованием специальной разводки платы или дополнительного внешнего буфера с соответствующей задержкой.

На приемном конце сигнал принимается дифференциальными LVDS-приемниками и подается на триггеры, которые защелкивают данные по принятому тактовому сигналу частотой 311 МГц.

Отметим, что использование такой высокой скорости передачи требует весьма тщательного подхода к выполнению схемы и к разводке печатной платы.

Благодаря своим высоким характеристикам интерфейс LVDS находит все большее применение в бюджетных разработках. Все большей популярностью пользуются наборы решений для замены параллельных TTL-линий высокоскоростным последовательным LVDS-каналом. Примером такого решения может служить набор MuxIt, выпускаемый Texas Instruments. Набор включает в себя три микросхемы:

- передатчик сериалайзер SN65LVDS151;

- приемник десериалайзер SN65 LVDS152;

- умножитель частоты SN65LVDS150.

На рис. 18 приведен простейший базовый вариант структуры системы на базе набора MuxIt.

Передатчиком SN65LVDS151 от 4 до 10 разрядов данных преобразуются в последовательный канал и передаются через LVDS-линк. Параллельный тактовый сигнал используется умножителем частоты SN65LVDS150 для генерирования скоростного тактового сигнала, который используется для передачи данных и передается на приемный конец системы по отдельному LVDS-линку. Сигналы M1…M5 используются для определения количества разрядов данных, преобразуемых в LVDS-канал. Параллельные данные загружаются в сдвиговый сигнал передатчика по низкочастотному тактовому сигналу. Из сдвигового сигнала данные выдаются в LVDS-линк по синтезированному умножителем частоты высокочастотному тактовому сигналу.

На приемном конце канала данные по принятому высокочастотному тактовому сигналу загружаются в сдвиговый регистр приемника SN65LVDS152, где приводятся к параллельному виду и выдаются на параллельные выходы данных D0 — D9. Принятый тактовый сигнал также используется умножителем частоты SN65LVDS150 для восстановления исходного низкочастотного тактового сигнала.Компоненты набора MuxIt образуют законченное решение для преобразования параллельной шины в LVDS-канал и обратно.

Показанная на рис. 18 конфигурация компонентов набора является простейшей базовой, но не единственной возможной конфигурацией канала. Умножитель частоты допускает коэффициент умножения до 40, что позволяет последовательно объединять в один канал до 4 сериалайзеров, преобразуя в один последовательный канал 40-разрядную параллельную шину. Кроме того, возможно параллельное подключение нескольких сериалайзеров и десериалайзеров для образования единого более скоростного линка с несколькими каналами данных и одним тактовым каналом. Сочетание параллельного и последовательного подключения элементов набора позволяет подобрать оптимальную конфигурацию системы для получения оптимального сочетания пропускной способности канала и количества линий передачи.Компоненты набора MuxIt могут поддерживать и многоточечный шинный режим работы.

Существуют и одночиповые решения, рассчитанные на фиксированную конфигурацию LVDS-канала. Примером такой пары для передачи точка — точка до 28 параллельных линий по пяти LVDS-каналам может служить пара из передатчика/сериалайзера SN65LVDS93 и приемника/десериалайзера SN65LVDS94.

Совместно эти две микросхемы образуют канал со скоростью передачи до 1,82 Гбит/c (именно 1,82 Гигабита в секунду, то есть 227,5 Мегабайта в секунду). При этом входная тактовая частота параллельной шины может достигать 65 МГц. Микросхемы SN54LVDS93/94 используют питание напряжением 3,3 В, но при этом их входы являются совместимыми с уровнями TTL- логики 0,5 В. Типичная потребляемая мощность в рабочем режиме составляет около 250 мВт.

Еще одним интересным решением по интеграции LVDS-каналов является предлагаемый TI набор из одиночных LVDS-приемника и LVDS-передатчика, каждый из которых выпускается в корпусе SOT-23, — SN65LVDS1/ S2/T2 (рис. 20).

Основные параметры передатчика:

- возможность горячего подключения;

- скорость обмена до 630 Мбит/с;

- типичная потребляемая мощность на частоте 200 МГц составляет 25 мВт;

- задержка передачи сигнала 1,7 нс;

- 5В-совместимые входы.

Основные параметры приемника:

- встроенный терминирующий резистор на 100 Ом;

- защита от обрывов по входу;

- скорость обмена до 400 Мбит/с;

- время задержки распространения сигнала — 1,7 нс.

Приемник и передатчик этой серии представляют собой законченные узлы, которые позволяют преобразовать к LVDS любую, даже одиночную линию.

Привет! Достаточно часто приходят на ремонт ноутбуки с проблемами вывода изображения на дисплей. Естественно нельзя списать все поломки связанные с выводом изображения исключительно на LVDS или EDP интерфейс. Но разобравшись и поняв принцип работы этого интерфейса, проверив его работу путем несложных измерений. Можно значительно упростить общую диагностику и снизить время, а также стоимость ремонта, исключив ошибочную покупку деталей. Для начала разберемся с теорией, что это вообще за интерфейс, кто придумал, как работает и в чем разница с более новым EDP интерфейсом.

Теория.

Что значит дифференциальная? Дифференциальная передача означает, что сигнал идет не в виде положительного напряжения относительно земли, а относительно инверсии самого себя на соседнем проводнике. Разница между проводниками пары и есть сигнал. Такой способ передачи показал наибольшую помехоустойчивость на больших скоростях передачи данных. Причем максимальное синфазное напряжение обычно 1.3V, что позволяет использовать LVDS во многих интегральных микросхемах, печатных платах, шлейфах с низким рабочим напряжением.

Дифференциальная передача сигнала используется в SCSI, Ethernet, PCI Express, HDMI, Display Port и даже в USB. Когда скорости одной пары недостаточно, возможно использование нескольких пар, этот принцип используется в PCI Express 1x — 16x. Где ширина шины (количество пар) диктует возможную скорость передачи.

Зная все это, не совсем корректно называть LVDS исключительно дисплейным интерфейсом. Это всего лишь метод передачи сигнала до дисплея используя гибкий провод или шлейф. Поэтому разъемы, шлейфы, матрицы различны по используемым типам подключения. Каждый производитель посчитал необходимым разработать свой тип сопряжения системной платы и дисплея. И что мы имеем — многообразие различных дисплеев, шлейфов, разъемов не подходящих друг к другу, но использующих один принцип передачи сигнала. Блин ребята, просто договоритесь…

Диагностика и ремонт LVDS интерфейса матрицы ноутбука, на практике.

Питающие напряжения.

Разобравшись с принципом работы шины данных LVDS, EDP и их отличием, далее расскажу об основных питающих напряжениях на примере матрицы AUO B156XW02.

Наиболее часто в ноутбуках для обеспечения работы дисплея используется условно 3 типа питающего напряжения:

- 6-21V (обычно VLED) питание подсветки матрицы. Чаще светодиодной — LED подсветки. А ранее, использовался инвертор — отдельная плата для преобразования низкого напряжение в высокое, необходимое для работы лампы подсветки CCFL. Наподобие бытовых люминесцентных энергосберегающих ламп.

- 3.3V (обычно VDD) питание электронных компонентов дисплея. Данное напряжение необходимо для работы активных компонентов панели, процессора и терминации внутренних шин панели.

- 3.3V (обычно VEDID) питание EDID — микросхема памяти, содержащая программный код описывающий характеристики панели — модель, разрешение, частота и другие параметры указывающие правильное конфигурирование видеосигнала.

Управляющие сигналы.

К управляющим сигналам можно отнести:

- SM шину по которой читается микросхема EDID (обычно это контакты CLK_EDID и DAT_EDID).

- Управление подсветкой это ее включение\выключение сигналом VLED_EN и уровень яркости подсветки VPWM_EN.

Сигнал включения подсветки (VLED_EN) представляет собой один контакт появление на котором напряжения, обычно 3.3V является логической единицей, что означает — подсветку включить. Если на этом контакте будет отсутствовать напряжение, подсветка матрицы не будет работать даже если подается основное напряжение на питание подсветки (VLED).

Яркость подсветки управляется шим сигналом (VPWM_EN). Уровень его напряжения составляет диапазон от 2.1V до 5.5V. А управление яркостью подсветки осуществляется изменением скважности импульсного сигнала. Отсутствие данного сигнала приводит к отключению подсветки.

Последовательность запуска.

Измерения.

Используя данные диаграммы представленной выше, можно понять последовательность запуска матрицы. Но стоит уточнить один момент, отсутствие напряжения VEDID и чтения микросхемы EDID приводит к отсутствию всех напряжений, и сигналов. Так как, системная плата не считала прошивку панели или матрицы. Исключением может быть напряжение VLED, для работы подсветки дисплея.

Если напряжение VEDID присутствует, микросхема EDID читается (обмен на CLK_EDID и DAT_EDID) а напряжение VDD отсутствует. Это свидетельствует о неверной микропрограмме записанной в матрице (EDID) или неисправной системной плате ноутбука, например узел формирования VDD.

В случае отсутствия чтения EDID. При наличии напряжения VEDID и отсутствии обрывов CLK_EDID и DAT_EDID. Скорее всего виновником поломки является видеопроцессор или видеочип на системной плате ноутбука, реже конвертер видеосигнала EDP-LVDS и другие микросхемы отвечающие за вывод видеосигнала. Все зависит от конкретной реализации системной платы.

И всегда, в диагностике и ремонте необходимо отталкиваться от особенностей реализации схемы системной платы и дисплея, по возможности разумеется.

Конвертеры и переключатели видеосигнала.

Конкуренция, продвижение более новых компонентов, энергосберегающих технологий толкает разработчиков компонентов и системных плат к использованию различных конвертеров, и переключателей видеосигнала. С переключателями вроде все более или менее понятно, если используется 2 видеопроцессора Intel и NVIDIA например, микросхема берет на себя роль переключателя и в нужный момент (при запуске игры) подключает матрицу к высокопроизводительному видеочипу. При переходе на питание с батареи — наоборот. Если на системной плате установлен переключатель, источником управляющих сигналов чаще всего являются оба видеопроцессора и все управляющие сигналы запараллелены.

Заключение.

В заключение из всего рассказанного выше, хочется напомнить, что данный материал носит ознакомительный характер и совсем не руководство к действиям. Думаю, эта статья поможет интересующимся и остановит от нежелательных действий безрассудно поверивших в свои силы. Расскажет об общих объемах работ и знаний, необходимых для выполнения ремонта ноутбуков с поломками связанными с выводом изображения.

Ставьте лайки, делайте репосты, подписывайтесь на мою группу вконтакте для получения актуальных постов. Спасибо за уделенное моей статье время, очень надеюсь что был полезен! Всем счастья!

В последнее время среди всевозможных шинных и интерфейсных решений все чаще выделяют скоростной и достаточно неприхотливый интерфейс LVDS. Его применение позволяет достичь скорости передачи до 400–600 Мбит/c по одной паре, причем практически без применения всевозможных экзотических элементов. В этой статье рассматривается не только сам интерфейс LVDS, но и вопросы его применения, построения LVDS-каналов и интеграцию их в состав устройства. Причем основное внимание уделяется не предельным показателям, достигнутым в лабораторных условиях, а именно рекомендациям по проектированию реальных решений на основе доступных компонентов, которые могут быть применены в реальных устройствах, чтобы помочь разработчикам в решении проблем.

Как вариант транспорта для межмодульного и межкорпусного обмена мы рассмотрим стремительно набирающий популярность интерфейс LVDS. Созданный как достаточно специфический стандарт обмена для подключения LCD-матриц в мобильных компьютерах, интерфейс LVDS показал себя недорогим и удобным решением. В его силах организация сверскоростного обмена между микросхемами на плате, минимизация количества линий за счет перевода из параллельной в последовательную передачу по LVDS, обеспечение скоростного межмодульного соединения на расстояние до нескольких метров по кабелю, организация скоростных шинных решений.

При этом LVDS-каналы не требуют каких-либо специфических и дорогостоящих материалов, а просто огранизуются на обычной печатной плате и работают по недорогим кабелям, таким как, например, широко известный и доступный кабель CAT5.

Рис. 1. Метод передачи интерфейса LVDS

Метод передачи

Интерфейс LVDS использует дифференциальную передачу сигналов с малыми сигнальными уровнями. На рис. 1 показана схема передачи одного канала LVDS. Передатчик управляет дифференциальной линией. В линию выдается токовая посылка с током 3,5 мА. Нагрузкой линии служат параллельно включенные дифференциальный LVDS-приемник и 100 Ом резистор. Сам приемник имеет высокое входное сопротивление, и основное формирование сигнала происходит на нагрузочном резисторе. При токе линии 3,5 мА на нем формируется падение напряжения 350 мВ, которое и детектируется приемником. При переключении направления тока в линии меняется полярность напряжения на нагрузочном резисторе, формируя состояния логического нуля и логической единицы.

Используемая схема передачи имеет целый ряд преимуществ.

LVDS-интерфейс имеет высокую скорость передачи данных. Определенная стандартом максимальная скорость составляет до 622 Мбит/с, что сравнимо с оптическим интерфейсом. При этом реальное быстродействие LVDS-канала ограничивается двумя факторами: скоростью подачи и съема данных и параметрами среды передачи.

Используемый дифференциальный метод передачи сигналов позволяет максимально снизить влияние внешних наводок. Малое изменение напряжения, симметричные линии передачи и низкое нарастание напряжения (1 В/нс) обусловливают малый уровень наводок от самого интерфейса. В свою очередь, малый уровень перекрестных наводок и низкая чувствительность к внешним наводкам позволяют использовать высокую плотность соединений как на печатной плате, так и в кабеле. Метод передачи LVDS не зависит от напряжения питания и работает при напряжении питания передатчика и приемника 5 В, 3 В или 2,5 В. При этом сопряжение устройств с разным напряжением питания не является проблемой.

Используемый метод передачи позволяет также существенно снизить энергопотребление интерфейса. На 100 Ом нагрузке LVDS при падении напряжения 400 мВ составляет 1,2 мВт. Для сравнения, интерфейс RS-422 имеет рассеиваемую мощность на нагрузке порядка 90 мВт, что в 75 раз больше.

Следует отметить и простоту терминирования сигнальных LVDS-линий — для этого требуется всего один резистор для каждой пары, и все. Для сравнения, другие скоростные методы требуют пары резисторов, один из которых подключается на землю, а второй к питанию, причем зачастую не напрямую, а через специальный источник.

LVDS-стандарт

LVDS-интерфейс описывается двумя стандартами: ANSI/TIA/EIA-644 и IEEE 1596.3. TIA-644 — общий стандарт. Он описывает электрическую часть интерфейса — выходные и входные параметры приемника. Стандарт не включает в себя функциональное описание, протокол обмена или полные характеристики кабеля, поскольку все это зависит от приложения.

Читайте также: